## EVERSOURCE MODEL AND TECHNICAL DATA REQUEST LIST FOR AFFECTED SYSTEM OPERATOR (ASO) TRANSMISSION STUDIES

In preparation for conducting the ASO studies, Eversource would like to provide customers with the list of technical information that will be needed in advance so that customers can begin pulling this information together. All data below will need to be received for each project before the ASO study can commence. It is assumed that all the DER included in the ASO transmission studies are non-FERC.

The modeling and data requests are for studies to support the ISO-NE Level 0 and Level 3 Proposed Plan Application (PPA).

All applications that are greater than 1MW <u>must provide</u> a fully working PSCAD model and the following inverter modeling information.

- A stamped one-line diagram, including total project size, GSU information, inverter manufacturer, inverter model name, version, number of inverters and kW rating.

- Presence of 32 or 32R Directional Power Relay to be included in one-line diagram if project has an export or import limit.

- Description of the Battery Energy Storage System (BESS) if the project includes any BESS.

- If the project includes both BESS and PV how are the BESS and PV connected (AC coupled, or DC coupled)?

- o Can the BESS charge from the grid?

- Energy Storage System (ESS) Questionnaire, if not submitted with application in powerclerk. A sample ESS questionnaire is included in Appendix F: Energy Storage System (ESS) Questionnaire.

- Fully functional PSCAD models of the projects are required. PSCAD model requirements are included in the attached Appendix C: PSCAD Model Requirements for the Eversource ASO Study.

- The inverter's frequency and voltage relay trip settings must meet the requirements found in the attached ISO-NE Default New England Bulk System Area Settings Requirement in Appendix D: ISO-NE Default New England Bulk System Area Settings Requirement.

- The PSCAD Model supplier checklist is included in Appendix E: PSCAD Model Checklist.

#### EVERSOURCE DATA AND MODEL REQUEST TO SUPPORT ISO-NE LEVEL 0 PPA APPROVAL

#### 1. PROJECT PHYSICAL INFORMATION

Stamped project one-line diagram (must include inverters)

#### 2. PROJECT MARKET INFORMATION

- Project projected in-service date.

- Project will indicate if it will be a Settlement Only Generator (SOG) or if it intends on participating in the ISO-NE market as a Generator in accordance to ISO-NE designation in OP-14<sup>1</sup>.

## EVERSOURCE DATA AND MODEL REQUEST FOR STUDY TO SUPPORT ISO-NE LEVEL 3 PPA APPROVAL

#### 1. PROJECT PHYSICAL INFORMATION

Stamped project one-line diagram (must include inverters)

#### 2. PROJECT MARKET INFORMATION

- Project projected in-service date

- Project will indicate if it will be a Settlement Only Generator (SOG) or if it intends on participating in the ISO-NE market as a Generator in accordance to ISO-NE designation in OP-14<sup>1</sup>.

#### 3. PROJECT TECHNICAL INFORMATION

- Conductor type and distances in mile between inverters/GSUs (collection system)

- Conductor type and length of dedicated feeder to POI in miles (generator tie-line)

- Generator step-up (GSU) transformer size (MVA), impedance (%Z), saturation data, winding configuration and X/R ratio

- GSU transformer number of taps and per unit size of each (typical is +/-2 steps, each at 2.5% or, 0.95, 0.975, 1.0,1.025, 1.05 per unit)

- Project inverter modeling information (>1MW and <5MW only)</li>

- Eversource to use the DER A inverter stability model

- Project inverter modeling information (≥5MW projects and single or multiple projects sharing the same POI)

- Datasheet and manual

- Reactive capability curve and/or data tables necessary to create the capability curve when the project output is a maximum (Pmax)

- Equivalent collection system impedance (per-unit quantity on 100MVA system base)

- Generator tie-line impedance (per-unit quantity on 100MVA system base)

- Stability model in PSS/E standard library model format. Note ISO-NE does not accept user- written models.

- The following PSSE v34 standard library renewable energy system models shall be used to represent the transient stability of inverter-based DER's

- Renewable Energy Generator/Converter Model: REGC\_B

- Renewable Energy Electrical Model: REEC D

- Centralized Plant Controller Model: REPC\_A (for standalone PV, BESS and PV+DC coupled BESS), PLNTBU1 + REAX4BU1 (for PV+AC coupled BESS and hybrid-projects which include multiple technologies controlled by a single plant controller)

| Project Type        | PSS/E Model Required |        |        |         |          |

|---------------------|----------------------|--------|--------|---------|----------|

| Project Type        | REGC_B               | REEC_D | REPC_A | PLNTBU1 | REAX4BU1 |

| Solar PV Only       | Χ                    | X      | X      |         |          |

| BESS Only           | Х                    | Х      | X      |         |          |

| PV+DC-Coupled BESS  | Х                    | Х      | Х      |         |          |

| PV+ AC-Coupled BESS | Х                    | Х      |        | Х       | Х        |

- Stability models must consist of the types listed in the latest version of the NERC List of

Acceptable Models for Interconnection-Wide Modeling, as required by the ISO New England

Compliance Bulletin MOD-032 dated September, 2022<sup>2</sup>. The NERC list of Acceptable

Renewable Energy Resource Models as of June 8, 2021 is listed in Appendix A: NERC List of

Acceptable Renewable Energy Resource Models as of 06/08/2021.

- The PSS/E stability model parameters are listed in Appendix B: PSS/E Stability Model Parameters.

- The stability model must include accurate voltage and frequency control parameters if the voltage and frequency control functions of the model are enabled according to DER planning's requirement.

- Comprehensive project inverter modeling information

- Description of the Battery Energy Storage System (BESS) if the project includes any BESS.

- If the project includes both BESS and PV how are the BESS and PV connected (AC coupled, or DC coupled)?

- Can the BESS charge from the grid?

- o Inverter manufacturer, inverter model name, version and kW rating.

- Fully functional PSCAD models of the projects are required. PSCAD model requirements are included in the attached Appendix C: PSCAD Model Requirements for the Eversource ASO Study.

- The inverter's frequency and voltage relay trip settings must meet the requirements found

in the attached ISO-NE Default New England Bulk System Area Settings Requirement in

Appendix D: ISO-NE Default New England Bulk System Area Settings Requirement

- The PSCAD Model supplier checklist is included in Appendix E: PSCAD Model Checklist.

- A benchmarking report between PSSE and PSCAD is required. Benchmarking requirements are included in the attached **Appendix G**.

<sup>&</sup>lt;sup>1</sup>ISO New England Operating Procedure No. 14 - Technical Requirements for Generators, Demand Response Resources, Asset Related Demands and Alternative Technology Regulation Resources

<sup>&</sup>lt;sup>2</sup> https://iso-ne.com/static-assets/documents/2015/06/iso\_new\_england\_compliance\_bulletin\_mod\_032.pdf

# Appendix A: NERC List of Acceptable Renewable Energy Resource Models as of 06/08/2021

The most-up-to-date list of NERC Acceptable Models can be found at: <a href="https://www.nerc.com/pa/RAPA/ModelAssessment/Documents/Acceptable%20Models%20List%E2%80%8B.xlsx">https://www.nerc.com/pa/RAPA/ModelAssessment/Documents/Acceptable%20Models%20List%E2%80%8B.xlsx</a>

## **Appendix B: PSS/E Stability Model Parameters**

## **REGC\_B Model Parameters - Model parameters are specified in per unit of machine MVA base**

|           | Typical Values or range of |                                                                                                                                            |                                                                                                       |

|-----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Parameter | value*                     | Description                                                                                                                                | Notes                                                                                                 |

| RateFlag  | 0 or 1                     | 0: rate limit on active current, 1: rate limit on active power                                                                             |                                                                                                       |

| PQFlag    | 0 or 1                     | PQ priority Flag; 0: Q priority,<br>1: P priority                                                                                          | PQFlag value must match the PQFlag value used in the REEC_D Model                                     |

| Тg        | 0.02                       | Tg (sec), Converter time constant (> 0)                                                                                                    |                                                                                                       |

| Tfltr     | 0.02                       | Tfltr(sec), Voltage filter time constant                                                                                                   |                                                                                                       |

| Iqrmax    | 1 - 999                    | Iqrmax (pu/s), Upper limit on rate of change for reactive current (> 0)                                                                    | DER are not allowed to control voltage. Hence, parameters are                                         |

| Iqrmin    | -1999                      | Iqrmin (pu/s), Lower limit on rate of change for reactive current (< 0)                                                                    | not relevant                                                                                          |

| rrpwr     | Inverter<br>Specific       | rrpwr (pu/s), ramp rate for<br>real power increase (or<br>decrease for the case of<br>battery in charging mode)<br>following a fault (> 0) | This must be set to inverters actual ramp rate and must be at least 2 pu/s as per IEEE 1547 standard. |

| Те        | 0.01                       | Te (s), time constant to model inner control loops                                                                                         |                                                                                                       |

| Imax      | 1.0 – 1.5                  | Imax (pu), Maximum current rating of the converter (> 0)                                                                                   | Imax value must match the Imax value used in the REEC_D Model                                         |

<sup>\*</sup> Typical Values are provided only for reference purposes and should not be interpreted as values that must be strictly used

REEC\_D Model Parameters - Model parameters are specified in per unit of machine MVA base

| Parameter | Typical Values<br>or range of<br>value* | Description                                                                                          | Notes                                                                                                                          |

|-----------|-----------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| PFFlag    | 0 or 1                                  | PFFLAG: • 1 if power factor control • 0 if Q control (which can be controlled by an external signal) | Must be set to 0 when using a plant controller model                                                                           |

| VFlag     | 0 or 1                                  | VFLAG: • 1 if Q control • 0 if voltage control                                                       | This flag is irrelevant when QFLAG is set to 0                                                                                 |

| QFlag     | 0 or 1                                  | QFLAG: • 1 if voltage or Q control • 0 if constant pf or Q control                                   | Must be set to 0 as DER's are not allowed to control voltage under normal operating conditions                                 |

| PFlag     | 0 or 1                                  | PFLAG: • 1 if active current command has speed dependency • 0 for no dependency                      | Must be set to 0 as there is no speed dependency                                                                               |

| PQFlag    | 0 or 1                                  | PQFLAG: • 1 for P priority • 0 for Q priority                                                        | PQFlag value must match the PQFlag value used in the REGC_B Model                                                              |

| VcmpFlag  | 0 or 1                                  | PQFLAG: • 1 for current compensation • 0 for reactive droop compensation                             | This flag is irrelevant when QFLAG is set to 0                                                                                 |

| Vdip      | <0.88                                   | Vdip (pu), low voltage threshold to activate reactive current injection logic                        |                                                                                                                                |

| Vup       | >1.1                                    | Vup (pu), Voltage above which reactive current injection logic is activated                          |                                                                                                                                |

| Trv       | 0.02                                    | Trv (s), Voltage filter time constant dbd1 (pu), Voltage error                                       |                                                                                                                                |

| dbd1      | -0.1 - 0                                | dead band lower threshold (≤0)  dbd2 (pu), Voltage error dead band upper threshold                   | Inverter specific values to be used if inverter provides dynamic voltage support in the low voltage mandatory operation region |

| dbd2      | 0 - 0.1                                 | (≥0)                                                                                                 | a.iaacoi j operation region                                                                                                    |

| Kqv   | Inverter<br>Specific | Kqv (pu), Reactive current injection gain during over and undervoltage conditions                                     |                                                                    |

|-------|----------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| lqh1  | 1                    | Iqh1 (pu), Upper limit on reactive current injection Iqinj                                                            |                                                                    |

| lql1  | -1                   | Iql1 (pu), Lower limit on reactive current injection Iqinj                                                            |                                                                    |

| Vref0 | 0                    | Vref0 (pu), User defined reference (if 0, model initializes it to initial terminal votlage)                           |                                                                    |

| Iqfrz | 0                    | Iqfrz (pu), Value at which Iqcmdbl (value of Iqcmd before limit) is held for Thld seconds after a voltage dip is over |                                                                    |

| Thld  | 0                    | Thid (s), Time for which iqcmdbl is frozen after the voltage dip is over                                              |                                                                    |

| Thld2 | Inverter<br>Specific | Thld2 (s) (≥0), Time for which Ipcmd and Ipmax are frozen after the voltage dip is over                               |                                                                    |

| Тр    | 0.02                 | Tp (s), Filter time constant for electrical power                                                                     | Inverter Specific                                                  |

| Qmax  | 0.4 - 1              | QMax (pu), Maximum value of the signal Qext or Vext                                                                   | Must be set to 0 as DER's are not allowed to control voltage under |

| Qmin  | -1 0.4               | QMin (pu) Minimum value of the signal Qext or Vext                                                                    | normal operating conditions                                        |

| VMAX  | 1.1                  | VMAX (pu), Maximum limit for voltage control                                                                          | These values are irrelevant when                                   |

| VMIN  | 0.9                  | VMIN (pu), Minimum limit for voltage control                                                                          | QFLAG is set to 0                                                  |

| Кqр   | Inverter<br>Specific | Kqp (pu), Reactive power regulator proportional gain                                                                  |                                                                    |

| Kqi   | Inverter<br>Specific | Kqi (pu), Reactive power regulator integral gain                                                                      |                                                                    |

| Kvp   | Inverter<br>Specific | Kvp (pu), Voltage regulator proportional gain                                                                         |                                                                    |

| Kvi   | Inverter<br>Specific | Kvi (pu), Voltage regulator integral gain                                                                             |                                                                    |

| Vbias | 0                    | Vbias (pu), User-defined bias (normally 0)                                                                            |                                                                    |

| Tiq      | 0.02                 | Tiq (s), Time constant on delay for block s4                                                  |                                                             |

|----------|----------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| dPmax    | 0 - 999              | dPmax (pu/s) (>0) Power reference maximum ramp rate                                           |                                                             |

| dPmin    | -999 - 0             | dPmin (pu/s) (<0) Power reference minimum ramp rate                                           |                                                             |

| PMAX     | 1                    | PMAX (pu), Maximum power limit                                                                |                                                             |

| PMIN     | 0                    | PMIN (pu), Minimum power limit                                                                |                                                             |

| lmax     | 1.0 - 1.5            | Imax (pu), Maximum limit on total converter current                                           | Imax value must match Imax parameter in the REGC_B model    |

| Tpord    | 0.02                 | Tpord (s), Power filter time constant                                                         |                                                             |

| Vq1 – 10 | Inverter<br>Specific | Vq1 - 10 (pu), VDL table vq-iq<br>pair (voltage)                                              |                                                             |

| lq1 – 10 | Inverter<br>Specific | lq1 - 10 (pu), VDL table vq-iq<br>pair (current)                                              |                                                             |

| Vp1 – 10 | Inverter<br>Specific | Vp1 - 10 (pu), VDL table vp-ip<br>pair (voltage)                                              |                                                             |

| lp1 – 10 | Inverter<br>Specific | lp1 - 10 (pu), VDL table vp-ip<br>pair (current)                                              |                                                             |

| rc       | N/A                  | rc (pu), Current compensation resistance                                                      |                                                             |

| Xc       | N/A                  | Xc (pu), Current compensation reactance                                                       | Parameter is irrelevant since                               |

| Tr1      | N/A                  | Tr1 (s), Time constant for reactive current compensation                                      | QFLAG is set to 0                                           |

| Кс       | N/A                  | Kc, Reactive current compensation gain                                                        |                                                             |

| Ke       | 0 - 1                | Ke, Scaling on Ipmin, (0 for generator, 0 <ke≤ 1="" for="" storage)<="" td=""><td></td></ke≤> |                                                             |

| Vblkl    | 0.5                  | Vblkl (pu), Voltage below which converter will block                                          | Trigger momentary cessation when voltage drops below 0.5 pu |

| Vblkh    | 1.1                  | Vblkh (pu), Voltage above which converter will block                                          | Trigger momentary cessation when voltage crosses 1.1 pu     |

|      |     | Tblk (s), time for which converter will remain blocked after voltage is within the range Vblkl < | Converter deblock delay after |

|------|-----|--------------------------------------------------------------------------------------------------|-------------------------------|

| Tblk | 0.1 | Vt_filt < Vblkh                                                                                  | exiting momentary cessation   |

<sup>\*</sup> Typical Values are provided only for reference purposes and should not be interpreted as values that must be strictly used.

## REPC\_A Model Parameters - Model parameters are specified in per unit of machine MVA base

To be used for stand-alone PV, BESS and DC coupled PV+BESS

| Parameter              | Typical Values or range of value* | Description                                                                                              | Notes                                                                      |

|------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Bus Num                |                                   | Bus number for voltage control; local control if 0                                                       |                                                                            |

| Branch Bus<br>Num From |                                   | Monitored branch FROM bus<br>number for line drop<br>compensation (if 0 generator<br>power will be used) |                                                                            |

| Branch Bus<br>Num To   |                                   | Monitored branch TO bus number for line drop compensation (if 0 generator power will be used)            |                                                                            |

| Branch Ckt<br>Id       |                                   | Branch circuit id for line drop compensation                                                             |                                                                            |

| VCFlag                 | 0 or 1                            | VCFlag: • 1 with line drop compensation • 0 with droop if power factor control                           | Irrelevant if RefFlag is 0                                                 |

| RefFlag                | 0 or 1                            | RefFLAG: • 0 Q control • 1 voltage control                                                               |                                                                            |

| Fflag                  | 0 or 1                            | Fflag: • 0 disable • 1 enable control                                                                    | Must be set to 1 to enable frequency control                               |

| Tfltr                  | 0.02                              | Tfltr, Voltage or reactive power measurement filter time constant (s)                                    | DER are not allowed to control voltage. Hence, parameters are not relevant |

| Кр    | Controller<br>Specific | Kp, Reactive power PI control proportional gain (pu)                                                     |

|-------|------------------------|----------------------------------------------------------------------------------------------------------|

| Ki    | Controller<br>Specific | Ki, Reactive power PI control integral gain (pu)                                                         |

| Tft   | 0                      | Tft, Lead time constant (s)                                                                              |

| Tfv   | 0.02                   | Tfv, Lag time constant (s)                                                                               |

| Vfrz  | < 0.9                  | Vfrz, Voltage below which State s2 is frozen (pu)                                                        |

| Rc    | 0                      | Rc, Line drop compensation resistance (pu)                                                               |

| Xc    | 0                      | Xc, Line drop compensation reactance (pu)                                                                |

| Кс    | Controller<br>Specific | Kc, Reactive current compensation gain (pu)                                                              |

| emax  | 999                    | emax, upper limit on deadband output (pu)                                                                |

| emin  | -999                   | emin, lower limit on deadband output (pu)                                                                |

| dbd1  | -0.01                  | dbd1, lower threshold for reactive power control deadband (<=0)                                          |

| dbd2  | 0.01                   | dbd2, upper threshold for reactive power control deadband (>=0)                                          |

| Qmax  | 0-0.4                  | Qmax, Upper limit on output of V/Q control (pu)                                                          |

| Qmin  | -0.4 - 0               | Qmin, Lower limit on output of V/Q control (pu)                                                          |

| Kpg   | Controller<br>Specific | Kpg, Proportional gain for power control (pu)                                                            |

| Kig   | Controller<br>Specific | Kig, Integral gain for power control (pu)                                                                |

| Тр    | 0.02                   | Tp, Real power measurement filter time constant (s)                                                      |

| fdbd1 | -0.0006                | fdbd1, Deadband for frequency control, lower threshold (specified as per unit frequency deviation) (<=0) |

| fdbd2 | 0.0006                 | fdbd2, Deadband for frequency control, upper threshold (specified as per unit frequency deviation) (>=0) |                                                                          |

|-------|------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| femax | 999                    | femax, frequency error upper limit (pu)                                                                  |                                                                          |

| femin | -999                   | femin, frequency error lower limit (pu)                                                                  |                                                                          |

| Pmax  | 1                      | Pmax, upper limit on power reference (pu)                                                                |                                                                          |

| Pmin  | 0 or -1                | Pmin, lower limit on power reference (pu)                                                                | Set 0 for non-BESS, non-AC coupled BESS Set -1 for BESS, AC coupled BESS |

| Tg    | 0.02                   | Tg, Power Controller lag time constant (s)                                                               |                                                                          |

| Ddn   | Controller<br>Specific | Ddn, reciprocal of droop for over-frequency conditions (pu)                                              | Standard droop setting is 5%.<br>Set as 20                               |

| Dup   | Controller<br>Specific | Dup, reciprocal of droop for under-frequency conditions (pu)                                             | Standard droop setting is 5%.<br>Set as 20                               |

<sup>\*</sup> Typical Values are provided only for reference purposes and should not be interpreted as values that must be strictly used.

## PLNTBU1 Model Parameters - Model parameters are specified in per unit of system MVA base

PLNTBU1 model to be used in conjunction with REAX4BU1 model for AC couples PV+BESS.

| Parameter              | Typical Values or range of value* | Description                                                                                     | Notes |

|------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|-------|

| Bus Num                |                                   | Bus number for voltage control; local control if 0                                              |       |

| Branch Bus<br>Num From |                                   | Monitored branch FROM bus number for line drop compensation (if 0 generator power will be used) |       |

| Branch Bus<br>Num To   |                                   | Monitored branch TO bus number for line drop compensation (if 0 generator power will be used)   |       |

| Branch Ckt<br>Id |                        | Branch circuit id for line drop compensation                                                                 |                                              |

|------------------|------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| VCFlag           | 0 or 1                 | <ul><li>VCFlag:</li><li>1 with line drop compensation</li><li>0 with droop if power factor control</li></ul> | Irrelevant if RefFlag is 0                   |

| RefFlag          | 0 or 1                 | RefFLAG: • 0 Q control • 1 voltage control                                                                   |                                              |

| Fflag            | 0 or 1                 | Fflag: • 0 disable • 1 enable control                                                                        | Must be set to 1 to enable frequency control |

| Tfltr            | 0.02                   | Tfltr, Voltage or reactive power measurement filter time constant (s)                                        |                                              |

| Кр               | Controller<br>Specific | Kp, Reactive power PI control proportional gain (pu)                                                         |                                              |

| Ki               | Controller<br>Specific | Ki, Reactive power PI control integral gain (pu)                                                             | DER are not allowed to control               |

| Tft              | 0.01                   | Tft, Lead time constant (s)                                                                                  | voltage. Hence, parameters are               |

| Tfv              | 0.02                   | Tfv, Lag time constant (s)                                                                                   | not relevant                                 |

| Vfrz             | < 0.9                  | Vfrz, Voltage below which State s2 is frozen (pu)                                                            |                                              |

| Rc               | 0                      | Rc, Line drop compensation resistance (pu of SBASE)                                                          |                                              |

| Xc               | 0                      | Xc, Line drop compensation reactance (pu of SBASE)                                                           |                                              |

| Кс               | 0                      | Kc, Reactive current compensation gain (pu)                                                                  |                                              |

| Emax             | 999                    | Emax, Upper limit on deadband output (pu)                                                                    |                                              |

| Emin             | -999                   | Emin, Lower limit on deadband output (pu)                                                                    |                                              |

| dbd1             | -0.01                  | DBD1, Lower threshold for reactive power control deadband (<=0)                                              |                                              |

| dbd2             | 0.01                   | DBD2, Upper threshold for reactive power control deadband (>=0)                                              |                                              |

| Qmax             | 0 - 0.4                | Qmax, Upper limit on output of V/Q control (pu)                                                              |                                              |

| Qmin  | -0.4 - 0               | Qmin, Lower limit on output of V/Q control (pu)        |                                                                          |

|-------|------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|

| Kpg   | Controller<br>Specific | Kpg, Proportional gain for power control (pu)          |                                                                          |

| Kig   | Controller<br>Specific | KIG, Integral gain for power control (pu)              |                                                                          |

| Тр    | 0.02                   | TP, Real power measurement filter time constant (s)    |                                                                          |

| Fdbd1 | -0.0006                | FDBD1, Deadband for frequency control, lower threshold | 36mHZ standard dead band (36mHz/60Hz)                                    |

| Fdbd2 | 0.0006                 | FDBD2, Deadband for frequency control, upper threshold | 36mHZ standard dead band<br>(36mHz/60Hz)                                 |

| Femax | 999                    | FEMAX, Frequency error upper limit (pu)                |                                                                          |

| Femin | -999                   | FEMIN, Frequency error lower limit (pu)                |                                                                          |

| Pmax  | Project Specific       | PMAX, Upper limit on power reference (pu)              | Must be greater of either PV or<br>BESS MVA rating on 100MVA<br>base     |

| Pmin  | Project Specific       | PMIN, Lower limit on power reference (pu)              | Set 0 for non-BESS, non-AC coupled BESS Set -1 for BESS, AC coupled BESS |

| Тg    | 0.02                   | TG, Power Controller lag time constant (s)             |                                                                          |

| Ddn   | Controller<br>Specific | DDN, Reciprocal of droop for over-frequency conditions | Standard droop setting is 5%. Set as 20                                  |

| Dup   | Controller<br>Specific | DUP, Reciprocal of droop for under-frequency condition | Standard droop setting is 5%. Set as 20                                  |

| MVA_P |                        | MVA_P, Plant Controller MVA<br>base - (Note 1)         | If set to 0, model parameters are assumed on 100MVA base                 |

<sup>\*</sup> Typical Values are provided only for reference purposes and should not be interpreted as values that must be strictly used.

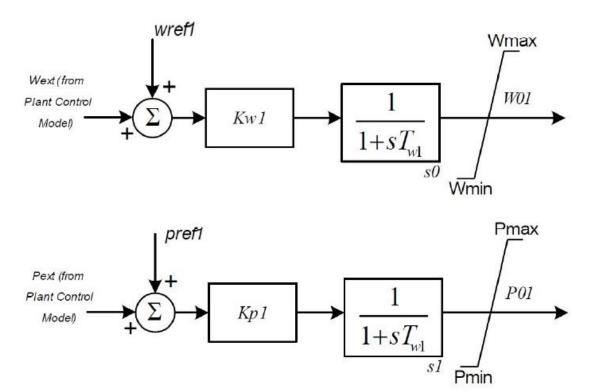

#### **REAX4BU1 Model Parameters**

To be used for AC coupled BESS projects and model parameters are in per unit of machine MVA base.

| Parameter | Typical Values or range of value* | Description                                                | Notes |

|-----------|-----------------------------------|------------------------------------------------------------|-------|

| Bus Num   |                                   | Bus Number at which the Plant controller Model is attached |       |

| Tw1  | Inverter Specific | Tw1 (s), Measurement time constant                  |                                                                            |  |

|------|-------------------|-----------------------------------------------------|----------------------------------------------------------------------------|--|

| Kw1  |                   | Kw1 (pu on MBASE), Gain for signal in reactive path | DER are not allowed to control voltage. Hence, parameters are not relevant |  |

| Kp1  |                   | Kp1 (pu on MBASE), Gain for signal in real path     |                                                                            |  |

| Wmax |                   | Wmax (pu), Maximum value of W01                     | DER are not allowed to control voltage. Hence, parameters are not relevant |  |

| Wmin |                   | Wmin (pu), Minimum value of W01                     |                                                                            |  |

| Pmax | 1                 | Pmax (pu), Maximum value of P01                     |                                                                            |  |

| Pmin | 0 or -1           | Pmin (pu), Minimum value of P01                     | Set 0 for PV<br>Set -1 for BESS                                            |  |

<sup>\*</sup> Typical Values are provided only for reference purposes and should not be interpreted as values that must be strictly used.

#### **Voltage and Frequency Protection Model Settings**

The following trip setting parameters are explained in more detail in the Default New England Bulk System Area Settings Requirements in **Appendix D**: ISO-NE Default New England Bulk System Area Settings Requirement.

| Parameter | Model   | Value | Description                    |

|-----------|---------|-------|--------------------------------|

| VL        |         | 0     |                                |

| VU        | VTGTPAT | 1.2   |                                |

| TP        |         | 0.16  | Over voltage trip setpoints    |

| VL        |         | 0     |                                |

| VU        | VTGTPAT | 1.1   |                                |

| TP        |         | 2     |                                |

| VL        |         | 0.88  |                                |

| VU        | VTGTPAT | 999   |                                |

| TP        |         | 3     | Under voltage trip setpoints   |

| VL        |         | 0.5   | Under voltage trip setpoints   |

| VU        | VTGTPAT | 999   |                                |

| TP        |         | 1.1   |                                |

| FL        |         | 0     |                                |

| FU        | FRQTPAT | 62    |                                |

| TP        |         | 0.16  | Over frequency trip setpoints  |

| FL        |         | 58.5  |                                |

| FU        | FRQTPAT | 61.2  | Under and over frequency trip  |

| TP        |         | 300   | setpoints                      |

| FL        |         | 56.5  |                                |

| FU        | FRQTPAT | 999   | Under frequency trip setpoints |

| TP        |         | 0.16  |                                |

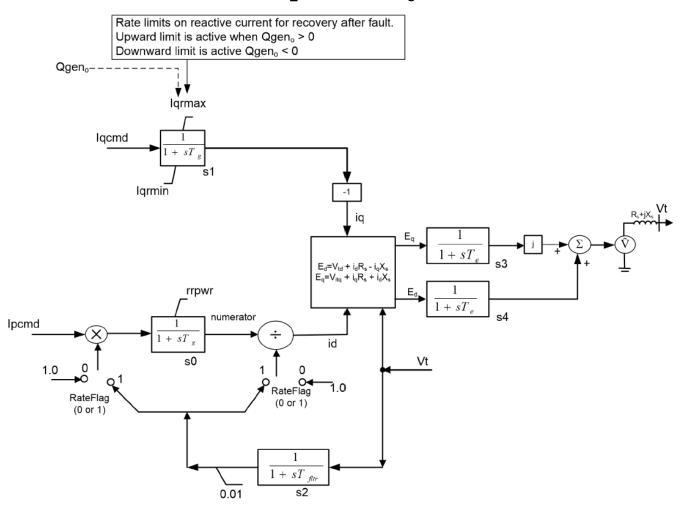

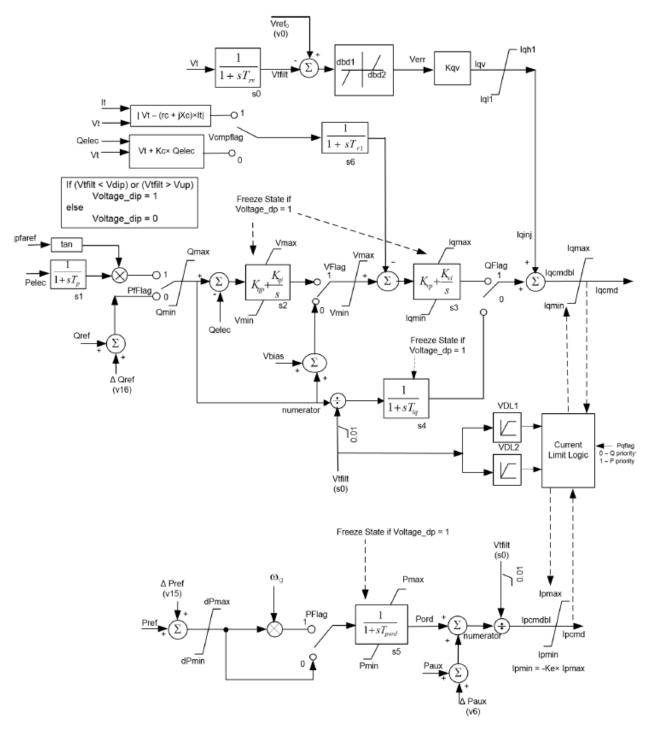

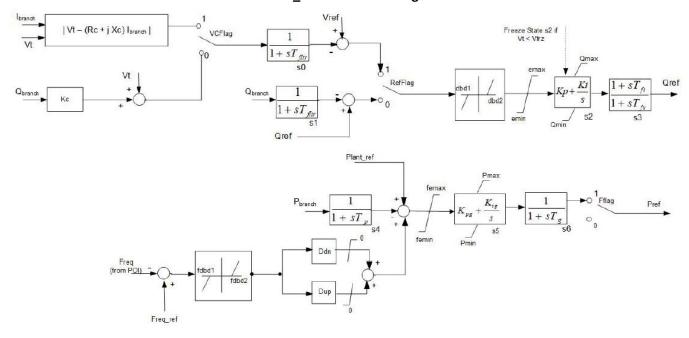

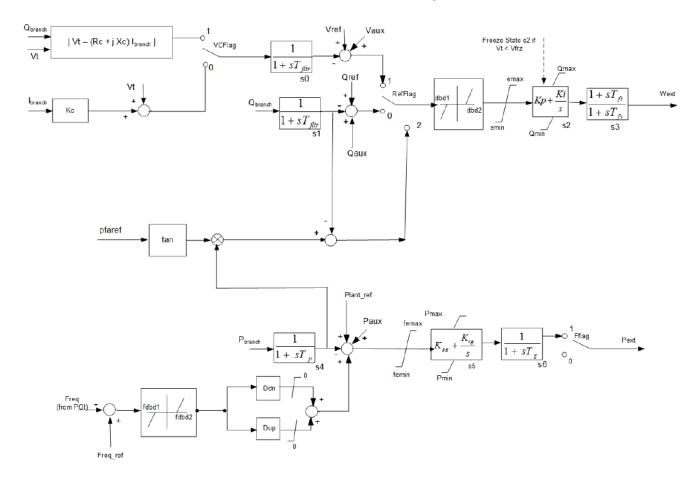

#### **PSS/E Stability Model Block Diagrams**

All block diagrams shown below originated from the PSSE Model Library.

## **REGC\_B Model Block Diagram**

## **REEC\_D Model Block Diagram**

## **REPC\_A Model Block Diagram**

#### **PLNTBU1 Model Block Diagram**

## **REAX4BU1 Model Block Diagram**

#### **Appendix C: PSCAD Model Requirements for the Eversource ASO Study**

#### General:

- 1. The developer/manufacturer of each DER project is responsible for providing a PSCAD model of the DER inverter, that meets all requirements listed in this document.

- **2.** It is strongly encouraged that the developer of the DER project require the manufacturer to provide this PSCAD model of the inverter.

- **3.** The developer/manufacturer is responsible for developing the "test case" referred to in Section *Inverter Model Usability Features requirement*, paragraph "I" of this document.

- **4.** In addition to the PSCAD model for the inverter itself, the developer must provide the following data for the rest of the facility:

- a. Single line diagram of the facility

- **b.** Winding configuration of GSU transformer (e.g. 0.6/13 kV transformer on eachinverter)

- c. Impedance of GSU transformer with MVA Base

- d. GSU Transformer Saturation Data

- e. Whether or not GSU is included in inverter PSCAD model

- f. Winding configuration of Plant transformer (e.g. 13 kV/34 kV transformer if one exists)

- g. Impedance of Plant transformer with MVABase

- **h.** Shunt capacitor size (MVAr) and number (ifany)

- i. DVAR size (MVAr) and number (if any)

- j. Controller details for DVAR and Shunt Capacitor coordination (if any)

#### Inverter Model Accuracy Features:

This section is based on 'PSCAD Model Requirements Rev 12' by Electranix Corporation and is modified by Eversource.

For the model to be sufficiently accurate, it must:

**A.** Represent the full detailed inner control loops of the power electronics. The model cannot use the same approximations classically used in transient stability modeling, and must fully represent all fast-inner controls, as implemented in the real equipment. Models which embed the actual hardware code into a PSCAD component are currently wide-spread, and this is the required type of model.<sup>4,5</sup>

<sup>&</sup>lt;sup>4</sup> The model must be a full power transistor (eg. IGBT) representation (preferred), or use an average source representation that approximates the switching but maintains full detail in the inner controls, and maintains DC side protection features. Models manually translated block-by-block from MATLAB or control block diagrams may be unacceptable because the method used to model the electrical network and interface to the controls may not be accurate, or portions of the controls such as PLL circuits or protection circuits may be approximated or omitted. Note that firmware code should be directly used to create an extremely accurate PSCAD model of the controls. The controller source code may be compiled into DLLs or binaries if the source code is unavailable due to confidentiality restrictions.

<sup>&</sup>lt;sup>5</sup> Model standards are under development which define appropriate ways to wrap .dll based control code into PSCAD models. Model writers are directed to this IEEE/Cigre WG to assist in developing a DLL standard for controller models.

- **B.** Represent all control features pertinent to the type of study being done. Examples include external voltage controllers, customized PLLs, ride-through controllers, SSCI damping controllers and others. As in point A, actual hardware code is required to be used for most control and protection features. Operating modes that require system specific adjustment must be user accessible.

- C. Represent plant level control. Power Plant Control (PPC) representation must be included which represents the specific controllers used in the plant. Plant controllers must be represented in sufficient detail to accurately represent short term performance, including specific measurement methods, communication time delays, transitions into and out of ride-through modes, settable control parameters or options, and any other specific implementation details which may impact plant behaviour. Generic PPC representations are not acceptable unless the final PPC controls are designed to exactly match the generic PPC model. If multiple plants are controlled by a common controller, or if the plant includes multiple types of IBRs (eg. Hybrid BESS/PV) this functionality must be included in the plant control model. If supplementary or multiple voltage control devices (eg. STATCOM) are included in the plant, these should be coordinated with the PPC.

- **D.** Represent all pertinent electrical and mechanical configurations. This includes any filters and specialized transformers. There may be other mechanical features such as gearboxes, pitch controllers, or others which should be modelled if they impact electrical performance within the timeframe of the study. Any control or dynamic features of the actual equipment which may influence behavior in the simulation period which are not represented or which are approximated should be clearly identified.

- **E.** Have all pertinent protections modeled in detail for both balanced and unbalanced fault conditions. Typically this includes various OV and UV protections (individual phase and RMS), frequency protections, DC bus voltage protections, converter overcurrent protections, and often other inverter specific protections. Any protections which can influence dynamic behavior or plant ride-through in the simulation period should be included. Actual hardware code is recommended to be used for these protection features.

- **F.** Be configured to match expected site-specific equipment settings. Any user tunable parameters or options must be set in the model to match the equipment at the specific site being evaluated, as far as they are known. Default parameters may not be appropriate unless these will match the configuration in the installed equipment.

#### **Inverter Model Usability Features:**

In order to allow study engineers to perform system analysis using the model, the PSCAD model must:

- **G.** Have control or hardware options which are pertinent to the study accessible to the user. Although plant must be configured to match site specific settings as far as they are known (see point F above), parameters pertinent to the study must be accessible for use by the model user. Examples of this could include protection thresholds, real power recovery ramp rates, frequency or voltage droop settings, voltage control response times, or SSCI damping controllers. Diagnostic flags (eg. flags to show control mode changes or which protection has been activated) should be visible to aid in analysis.

- **H.** Be accurate when running at a simulation time step of 10  $\mu$ s or higher. Often, requiring a smaller time step means that the control implementation has not used the interpolation features of PSCAD, or is using inappropriate interfacing between the model and the larger network. Lack of interpolation support introduces inaccuracies into the model at larger simulation time-steps. In cases where the power transistor (eg. IGBT) switching frequency is so high that even interpolation

does not allow accurate switching representation at 10  $\mu s$  (eg. switching frequency greater than 40 kHz), an average source approximation of the inverter switching may be used to allow a larger simulation time step<sup>4</sup>.

- 1. Operate at a range of simulation time steps. The model must not be restricted to operating at a single time step, but must be able to operate within a range (eg.  $10 \mu s 20 \mu s$ )

- J. Include documentation and a sample implementation test case. Test case models must be configured according to the site-specific real equipment configuration up to the Point of Interconnection. This would include (for example): aggregated generator model, aggregated generator transformer, equivalent collector branch, main plant transformers, gen tie line, power plant controller, and any other static or dynamic reactive resources. Test case must use a single machine infinite bus representation of the system, configured with an appropriate representative SCR<sup>7</sup>. Access to technical support engineers is desirable. Additional detail on required documentation and test case is described in PSCAD Model Test Checklist Appendix E: PSCAD Model Checklist.

- **K.** Have an identification mechanism for configuration. The model documentation must provide a clear way to identify the specific settings and equipment configuration which will be used in any study, such that during commissioning the settings used in the studies can be checked. This may be control revision codes, settings files, or a combination of these and other identification measures.

- L. Accept external reference variables. This includes real and reactive power ordered values for Q control modes, or voltage reference values for voltage control modes. Model must accept these reference variables for initialization, and be capable of changing these reference variables mid-simulation, ie. dynamic signal references.

- M. Be capable of initializing itself. Once provided with initial condition variables, the model must initialize and ramp to the ordered output without external input from simulation engineers. Any slower control functions which are included (such as switched shunt controllers or power plant controllers) must also accept initial condition variables if required. Note that during the first few seconds of simulation (eg. 0-2 seconds), the system voltage and corresponding terminal conditions may deviate from nominal values due to other system devices initializing, and the model must be able to tolerate these deviations or provide a variable initialization time.

- **N.** Have the ability to scale plant capacity. The active power capacity of the model must be scalable in some way, either internally or through an external scaling component<sup>8</sup>. This is distinct from a dispatchable power order, and is used for modeling different capacities of plant or breaking a lumped equivalent plant into smaller composite models.

- O. Have the ability to dispatch its output to values less than nameplate. This is distinct from scaling a plant from one unit to more than one, and is used for testing plant behaviour at various operating points.

- **P.** *Initialize quickly.* Model must reach its ordered initial conditions as quickly as possible (for example <5 seconds) to user supplied terminal conditions.

<sup>&</sup>lt;sup>6</sup> Care must be taken to ensure that any user-settable options are not changed in a way that is not implementable in the real hardware, and that any selectable options are actually available at the specific site being considered. Discussion is recommended with the manufacturer prior to any changes being made in model configuration.

<sup>&</sup>lt;sup>7</sup> Representative SCR should reflect approximate N-1 interconnection SCR where possible, especially if the system is expected to be weak. If the system strength is not known, using a relatively low SCR in the test system, such as 2.5, may help to avoid issues during study phases.

<sup>&</sup>lt;sup>8</sup> A free publicly available scaling transformer suitable for this purpose is available in the E-Tran library.

#### **Study Efficiency Features:**

The following elements are required to improve study efficiency, model compatibility, and enable other studies which include the model to be run as efficiently as possible

- Q. Model must be compatible with Intel Fortran compiler versions 15 and higher.<sup>9</sup>

- **R.** Model must be compatible with PSCAD version 4.6.3 and higher.

- **S.** Model must support multiple instances of its own definition in the same simulation case.

- T. Model must support the PSCAD "timed snapshot" feature accessible through project settings.

- **U.** Model must support the PSCAD "multiple run" feature.

- V. Model must not use or rely upon global variables in the PSCAD environment.

- W. Model must not utilize multiple layers in the PSCAD environment, including 'disabled' layers.

- X. Model must be compiled with Visual Studio 2015 or newer<sup>10</sup>

<sup>&</sup>lt;sup>9</sup> Models compiled using PSCAD with Intel Fortran 12 or 14 will use Visual Studio 2010 or 2013 which may cause compiler conflicts when those models are used in combination with models built with Intel Fortran 15 and newer. If Intel Fortran 12 or 14 support is required, it is recommended to compile both an Intel Fortran 12 to 14 model and an Intel Fortran 15 and newer model for maximum compatibility.

<sup>&</sup>lt;sup>10</sup>Older models which were compiled using Intel Fortran 12 may not be compatible with Visual Studio versions 2015 or newer. In this case older versions of Visual Studio may be needed.

## Appendix D: ISO-NE Default New England Bulk System Area Settings Requirement

The ISO-NE Default New England Bulk System Area Settings Requirements can be found here: <a href="https://www.eversource.com/content/docs/default-source/builders-contractors/ISO-NE Default NE Bulk System Area Settings.pdf">https://www.eversource.com/content/docs/default-source/builders-contractors/ISO-NE Default NE Bulk System Area Settings.pdf</a>

#### **Appendix E: PSCAD Model Checklist**

This document is a model requirements checklist which must be completed by the supplier of the model and submitted alongside each PSCAD model. Model suppliers must review every item in the checklist and indicate compliance for each item. If the supplied model does not meet any of the requirements an explanation of the deficiency must be provided in the comments column.

| Model Submission Summary (to be completed by model supplier) |  |  |  |

|--------------------------------------------------------------|--|--|--|

| Submission date:                                             |  |  |  |

| Project Name:                                                |  |  |  |

| Primary contact information for                              |  |  |  |

| model related questions:                                     |  |  |  |

| Secondary contact information                                |  |  |  |

| for model related questions:                                 |  |  |  |

| Manufacturer:                                                |  |  |  |

| Equipment type: (eg. PV or BESS)                             |  |  |  |

| Equipment version:                                           |  |  |  |

| Documentation file(s):                                       |  |  |  |

| Model Files supplied:                                        |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

|                                                              |  |  |  |

| Model Requirements Checklist |                                                                                                                                                                                                                                                                                                 | Reference | Model<br>Complies?<br>(Yes/No) | Comments |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------|----------|

| 1                            | Model Accuracy Features                                                                                                                                                                                                                                                                         |           |                                |          |

| 1.1                          | Power electronic controls are modelled by interfacing with actual firmware code from the inverter ("real code" model)                                                                                                                                                                           | A,B       |                                |          |

| 1.2                          | Operating modes which require system specific adjustment are accessible.                                                                                                                                                                                                                        | В         |                                |          |

| 1.3                          | Plant level controller is included according to inverter model accuracy features. 11                                                                                                                                                                                                            | С         |                                |          |

| 1.4                          | Model is capable of controlling frequency <sup>12</sup>                                                                                                                                                                                                                                         | B,C       |                                |          |

| 1.5                          | Includes pertinent electrical and mechanical features, such as gearboxes, pitch controllers, or other features which impact the plant performance in the simulation period. <sup>13</sup>                                                                                                       | D         |                                |          |

| 1.6                          | All protections which could impact ride-through performance are modelled in detail and adhrere to ISO-NE Default Bulk System Area Settings Requirement.                                                                                                                                         | E         |                                |          |

| 1.7                          | Model is configured for the specific site being evaluated, as far as they are known.                                                                                                                                                                                                            | F         |                                |          |

| 2                            | Model and Project Documentation                                                                                                                                                                                                                                                                 |           |                                |          |

| 2.1                          | Model includes documentation.                                                                                                                                                                                                                                                                   | J         |                                |          |

| 2.2                          | Documentation includes instruction for setup and running the model. The Vendor's name and the specific version of the model must be clearly observable in the .pscx PSCAD case. Documentation and supporting model filenames must not conflict with model version shown in the .pscx case file. | J         |                                |          |

| 2.3                          | Model is supplied with a sample test case including site specific plant representation.                                                                                                                                                                                                         | J         |                                |          |

| 2.4                          | Plant single line diagram is provided, and aligns with model                                                                                                                                                                                                                                    | J         |                                |          |

| 2.5                          | Model documentation provides a clear way to identify site-<br>specific settings and equipment configuration.                                                                                                                                                                                    | К         |                                |          |

| 3    | Model Usability Features                                                                                                                                   |   |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| 3.01 | Control or hardware options are accessible to the user as applicable.                                                                                      | G |  |

| 3.02 | Diagnostic flags are visible to the user.                                                                                                                  | G |  |

| 3.03 | Model uses a timestep greater than 10 μs.                                                                                                                  | Н |  |

| 3.04 | Model allows a range of simulation timesteps (ie. not restricted to a single timestep).                                                                    | I |  |

| 3.06 | Model accepts external reference variables for active and reactive power and voltage setpoint, and these may be changed dynamically during the simulation. | L |  |

| 3.07 | Model is capable of initializing itself.                                                                                                                   | М |  |

| 3.08 | Active power capacity is scalable.                                                                                                                         | N |  |

| 3.09 | Active power is dispatchable.                                                                                                                              | 0 |  |

| 3.10 | Model reaches setpoint P, Q, and V in 5 seconds or less                                                                                                    | Р |  |

| 3.11 | Model compatible with Intel FORTRAN version 15 and higher.                                                                                                 | Q |  |

| 3.12 | Model compiles using PSCAD version 4.5.3 or higher.                                                                                                        | R |  |

| 3.13 | Model supports multiple instances of its own definition in a single PSCAD case.                                                                            | S |  |

| 3.14 | Model supports PSCAD "snapshot" feature.                                                                                                                   | Т |  |

| 3.15 | Model supports the PSCAD "multiple run" feature.                                                                                                           | U |  |

| 3.16 | Model does not use PSCAD global variables.                                                                                                                 | V |  |

| 3.17 | Model does not use PSCAD layer functionality                                                                                                               | W |  |

| 3.18 | Model is compiled using MS Visual Studio v.2015 or newer                                                                                                   | Х |  |

<sup>&</sup>lt;sup>11</sup> If the plant is part of a multi-plant control scheme, a description of the overall scheme must be provided, and corresponding PPC models must be configured to control multiple plants accordingly.

<sup>&</sup>lt;sup>12</sup> Frequency control model requirements may vary by region. Example response time may be less than 10 seconds.

<sup>&</sup>lt;sup>13</sup> Simulation period may vary depending on the model use, but 10 seconds of simulation following an event such as a fault is a typical period.

#### **Appendix F: Energy Storage System (ESS) Questionnaire**

The ESS Questionnaire can be found here:

https://www.eversource.com/content/docs/default-source/builders-contractors/ESS Questionnaire.xlsx

#### Appendix G: Benchmarking reports for DER projects >=5MW

Benchmarking- Compare the voltage, active power (P), and reactive power (Q) at the terminal bus of the project and the point of interconnection (POI) bus for the following tests. All tests will be conducted using a generic source impedance for testing, flat-run and ringdown tests should be performed with a short-circuit ratio (SCR) of 2.5 and an X/R ratio of 10. If the inverter failed to initialize properly using SCR of 2.5, document the minimum SCR required for proper initialization. Over-frequency, Under-frequency, Over-voltage, Under-voltage tests should be performed with a high SCR (eg. 1000) in order to maintain voltage at the specified magnitudes and durations.

Flat Run Test: Run the project at its maximum output in both PSSE and PSCAD software under normal conditions, with the POI frequency set at 60Hz and voltage at 1 per unit (p.u.).

Ringdown Test: Initiate the simulation at normal conditions, with the POI frequency set at 60Hz and voltage at 1 p.u. Simulate a three-phase fault at the project's POI bus, lasting for 6 cycles, starting at 10 seconds. Continue the simulation until 30 seconds.

Over-frequency Test: Begin the simulation at normal conditions, with the POI frequency set at 60Hz and voltage at 1 p.u. Increase the frequency to 61.5Hz with Rate of change of frequency (ROCOF) of 3Hz/s at the project's POI bus, starting at 10 seconds. Maintain the frequency at 61.5Hz for 2 seconds. Continue the simulation until 30 seconds.

Under-frequency Test: Start the simulation at normal conditions, with the POI frequency set at 60Hz and voltage at 1 p.u. Decrease the frequency to 57Hz with ROCOF of 3Hz/s at the project's POI bus, starting at 10 seconds. Maintain the frequency at 57Hz for 2 seconds, Continue the simulation until 30 seconds.

Over-Voltage Test: Commence the simulation at normal conditions, with the POI frequency set at 60Hz and voltage at 1 p.u. Simulate an over-voltage event (1.125 p.u.) at the project's POI bus for 1 second, starting at 10 seconds. Then, decrease the voltage to 1.08 p.u. at the POI bus until 30 seconds.

Under-Voltage Test: Start the simulation at normal conditions, with the POI frequency set at 60Hz and voltage at 1 p.u. Simulate an under-voltage event (0.45 p.u.) at the project's POI bus for 1 second, starting at 10 seconds. Then, increase the voltage to 0.55 p.u. at the POI bus for 2 seconds, followed by an increase to 0.9 p.u. at the POI bus until 30 seconds.

For the battery energy storage system (BESS) project, the above tests need to be performed in both discharging and charging modes.

The expected acceptable benchmarking results should demonstrate a reasonable match between the voltage (V), active power (P), and reactive power (Q) values obtained from both PSSE and PSCAD simulations.